抗干擾問題是現(xiàn)代PCB設(shè)計(jì)中一個(gè)很重要的環(huán)節(jié),它直接反映了整個(gè)系統(tǒng)的性能和工作的可靠性�。對PCB設(shè)計(jì)工程師來說���,抗干擾設(shè)計(jì)是大家必須要掌握的重點(diǎn)和難點(diǎn)。

PCB板中干擾的存在

在實(shí)際研究中發(fā)現(xiàn),PCB板的設(shè)計(jì)主要有四方面的干擾存在:電源噪聲、傳輸線干擾�����、耦合和電磁干擾(EMI)�。

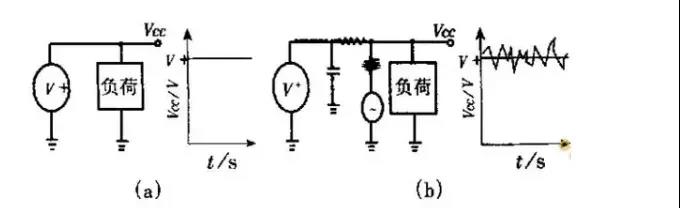

1. 電源噪聲

高頻電路中�����,電源所帶有的噪聲對高頻信號(hào)影響尤為明顯�����。因此,首先要求電源是低噪聲的��。在這里,干凈的地和干凈的電源同樣重要�。

電源特性

2. 傳輸線

在PCB中只可能出現(xiàn)兩種傳輸線:帶狀線和微波線�,傳輸線最大的問題就是反射,反射會(huì)引發(fā)出很多問題���,例如負(fù)載信號(hào)將是原信號(hào)與回波信號(hào)的疊加����,增加信號(hào)分析的難度�;反射會(huì)引起回波損耗(回?fù)p)��,其對信號(hào)產(chǎn)生的影響與加性噪聲干擾產(chǎn)生的影響同樣嚴(yán)重。

3. 耦合

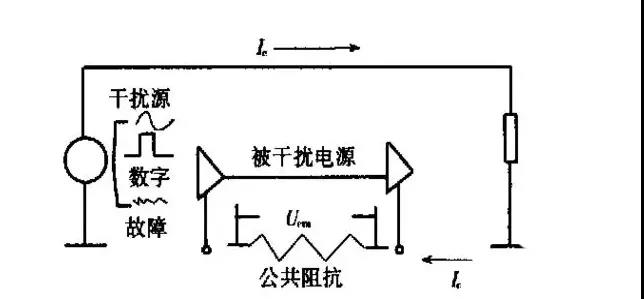

干擾源產(chǎn)生的干擾信號(hào)是通過一定的耦合通道對電控系統(tǒng)發(fā)生電磁干擾作用的��。

干擾的耦合方式無非是通過導(dǎo)線�����、空間���、公共線等作用在電控系統(tǒng)上。分析下來主要有以下幾種:直接耦合��、公共阻抗耦合�、電容耦合、電磁感應(yīng)耦合���、輻射耦合等�����。

公共阻抗耦合

4. 電磁干擾(EMI)

電磁干擾EMI有傳導(dǎo)干擾和輻射干擾兩種��。傳導(dǎo)干擾是指通過導(dǎo)電介質(zhì)把一個(gè)電網(wǎng)絡(luò)上的信號(hào)耦合(干擾)到另一個(gè)電網(wǎng)絡(luò)��。

輻射干擾是指干擾源通過空間把其信號(hào)耦合(干擾)到另一個(gè)電網(wǎng)絡(luò)�。

在高速PCB及系統(tǒng)設(shè)計(jì)中�����,高頻信號(hào)線�����、集成電路的引腳�、各類接插件等都可能成為具有天線特性的輻射干擾源,能發(fā)射電磁波并影響其他系統(tǒng)或本系統(tǒng)內(nèi)其他子系統(tǒng)的正常工作�。

PCB設(shè)計(jì)抗干擾措施

印制電路板的抗干擾設(shè)計(jì)與具體電路有著密切的關(guān)系,接下來���,我們僅就PCB抗干擾設(shè)計(jì)的幾項(xiàng)常用措施做一些說明����。

1. 電源線設(shè)計(jì)

根據(jù)印制線路板電流的大小����,盡量加租電源線寬度,減少環(huán)路電阻�����。同時(shí)�、使電源線、地線的走向和數(shù)據(jù)傳遞的方向一致���,這樣有助于增強(qiáng)抗噪聲能力���。

2. PCB設(shè)計(jì)地線設(shè)計(jì)的原則

(1)數(shù)字地與模擬地分開�。若線路板上既有邏輯電路又有線性電路,應(yīng)使它們盡量分開��。低頻電路的地應(yīng)盡量采用單點(diǎn)并聯(lián)接地��,實(shí)際布線有困難時(shí)可部分串聯(lián)后再并聯(lián)接地��。高頻電路宜采用多點(diǎn)串聯(lián)接地���,地線應(yīng)短而租�,高頻元件周圍盡量用柵格狀大面積地箔。

(2)接地線應(yīng)盡量加粗�。若接地線用很紉的線條,則接地電位隨電流的變化而變化��,使抗噪性能降低��。因此應(yīng)將接地線加粗��,使它能通過三倍于印制板上的允許電流�����。如有可能�����,接地線應(yīng)在2~3mm以上����。

(3)接地線構(gòu)成閉環(huán)路���。只由數(shù)字電路組成的印制板,其接地電路布成團(tuán)環(huán)路大多能提高抗噪聲能力���。

3. 退藕電容配置

PCB設(shè)計(jì)的常規(guī)做法之一是在印制板的各個(gè)關(guān)鍵部位配置適當(dāng)?shù)耐伺弘娙荨M伺弘娙莸囊话闩渲迷瓌t是:

(1)電源輸入端跨接10 ~100uf的電解電容器�����。如有可能����,接100uF以上的更好。

(2)原則上每個(gè)集成電路芯片都應(yīng)布置一個(gè)0.01pF的瓷片電容����,如遇印制板空隙不夠,可每4~8個(gè)芯片布置一個(gè)1 ~ 10pF的鉭電容��。

(3)對于抗噪能力弱�、關(guān)斷時(shí)電源變化大的器件,如 RAM�����、ROM存儲(chǔ)器件,應(yīng)在芯片的電源線和地線之間直接接入退藕電容�。

(4)電容引線不能太長,尤其是高頻旁路電容不能有引線�����。

4. PCB設(shè)計(jì)中消除電磁干擾的方法

(1)減小環(huán)路:每個(gè)環(huán)路都相當(dāng)于一個(gè)天線��,因此我們需要盡量減小環(huán)路的數(shù)量�����,環(huán)路的面積以及環(huán)路的天線效應(yīng)���。確保信號(hào)在任意的兩點(diǎn)上只有唯一的一條回路路徑���,避免人為環(huán)路,盡量使用電源層����。

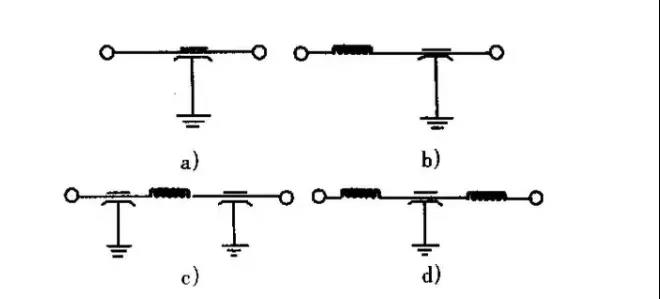

(2)濾波:在電源線上和在信號(hào)線上都可以采取濾波來減小EMI,方法有三種:去耦電容����、EMI濾波器�����、磁性元件��。

濾波器的類型

(3)屏蔽���。

(4)盡量降低高頻器件的速度。

(5)增加PCB板的介電常數(shù)��,可防止靠近板的傳輸線等高頻部分向外輻射���;增加PCB板的厚度,盡量減小微帶線的厚度��,可以防止電磁線的外溢����,同樣可以防止輻射。

深圳宏力捷電子電路板設(shè)計(jì)能力

最高信號(hào)設(shè)計(jì)速率:10Gbps CML差分信號(hào)�;

最高PCB設(shè)計(jì)層數(shù):40層;

最小線寬:2.4mil����;

最小線間距:2.4mil��;

最小BGA PIN 間距:0.4mm�����;

最小機(jī)械孔直徑:6mil���;

最小激光鉆孔直徑:4mil;

最大PIN數(shù)目:����;63000+

最大元件數(shù)目:3600;

最多BGA數(shù)目:48+���。

PCB設(shè)計(jì)服務(wù)流程

1. 客戶提供原理圖咨詢PCB設(shè)計(jì)���;

2. 根據(jù)原理圖以及客戶設(shè)計(jì)要求評估報(bào)價(jià);

3. 客戶確認(rèn)報(bào)價(jià)�����,簽訂合同�����,預(yù)付項(xiàng)目定金;

4. 收到預(yù)付款�,安排工程師設(shè)計(jì);

5. 設(shè)計(jì)完成后��,提供文件截圖給客戶確認(rèn)�;

6. 客戶確認(rèn)OK,結(jié)清余款�����,提供PCB設(shè)計(jì)資料�����。

深圳宏力捷推薦服務(wù):PCB設(shè)計(jì)打樣 | PCB抄板打樣 | PCB打樣&批量生產(chǎn) | PCBA代工代料